Топ-тенденции дизайна ванной комнаты на 2024 год Вот несколько топ-тенденций дизайна ванной комнаты на 2024 год: Эти тенденции отражают стремление к комфорту, функциональности и стилю в дизайне ванных комнат на 2024 год. Интерьер ванной: модные стили и интерьерные решения В 2024 году в области дизайна ванных комнат наблюдаются несколько модных стилей и интерьерных решений: Эти […]

Трендовые цвета

Светлый интерьер

Темный интерьер

Еще больше идей

Дом — это не просто место, где мы живем, это наше убежище, наша личная территория, где мы проводим большую

Цвет спальни: бежевая спальня – универсальный вариант? Бежевые краски для стен, мебель, текстиль, украшения

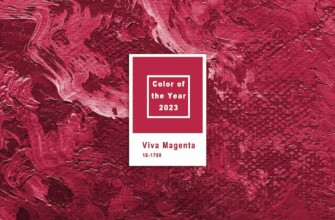

В 2023 году самым популярным цветом по версии института Pantone будет Viva Magenta, т.е. темно-красный

Модные в 2023 году цвета стен – это разнообразная палитра, в которой вы найдете как приглушенные оттенки

Покупка нового ковра часто может являться крупной инвестицией и выглядеть не совсем бюджетно.

Компания PPG уже выбрала свой цвет 2023 года. Оттенок Vining Ivy на границе синего и зеленого напоминает

Цвета земли в интерьерах используются уже на протяжении нескольких лет подряд. Все благодаря тому, что

Цвет стен на кухне обычно подбирают таким образом, чтобы он сочетался с мебелью и другими элементами